Recent Posts

How to Go Back to Work After Deep Vein Thrombosis – 2023 Guide

Deep Vein Thrombosis or DVT is one of the health diseases many people around the world experience. Unfortunately, it is not one of the...

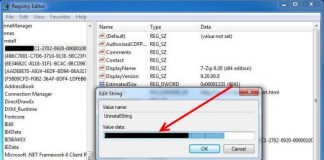

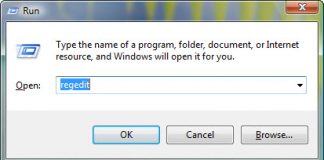

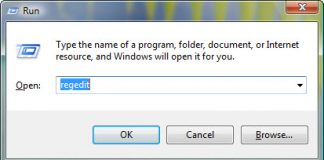

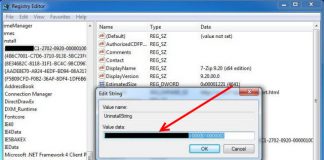

Uninstall and Remove iSEEK AnswerWorks English Step by Step – 2023 Guide

Do you need to remove the English runtime from iSEEK AnswerWorks to solve some problems? Are you looking for an effective solution to completely...

Uninstall and Remove the Legends League Step by Step – 2023 Guide

You have to remove League of Legends to solve some problems? Are you looking for an effective solution to completely delete all files from...

Uninstall and Delete Nexus Mod Manager Step by Step – 2023 Guide

Do you need to uninstall Nexus Mod Manager to fix some issues? Are you looking for an effective solution to completely delete all files...

Uninstall and Delete Numpy 1.6.1 Step by Step – 2023 Guide

Do you need to uninstall Numpy 1.6.1 to fix some problems? Are you looking for an effective solution to completely delete all files from...